迷茫了几天,痛苦了几天,今天终于把CRC循环编码的Verilog代码搞定了,也许是心情好转的缘故吧,不管怎么说,终究是做出来了,之前写的代码,也没找出是什么原因,不管输入什么,编码输出总是同一码元,郁闷~~今天重新写了一遍,原理还是一样,结果却是意料之中的,不管了,以后有时间再找原因吧,现在把写好的代码分享一下,希望大家提出意见

Verilog代码如下:

module code_crc(clk,reset,data,out);

input clk,reset;

input[7:0] data;

output[15:0] out;

reg[15:0] out;

//变量声明

reg[16:0] s;

integer i;

always@(posedge clk)

begin

if(!reset)

begin

s=17'b0;

out=16'b0;

end

else

begin

s={data[7:0],9'b0};

begin

for(i=7;i>0;i=i-1)

begin

if(s[16]==0) //若第一位为0,左移一位;

s=s<<1;

else begin

s=s^17'b11000000000000101;/*若第一位为1,则与生成多项式进行异或操作;*/

s=s<<1; //左移一位;

end

end

out=s[15:0]; //s的后16位即为校验位;

end

end

end

endmodule

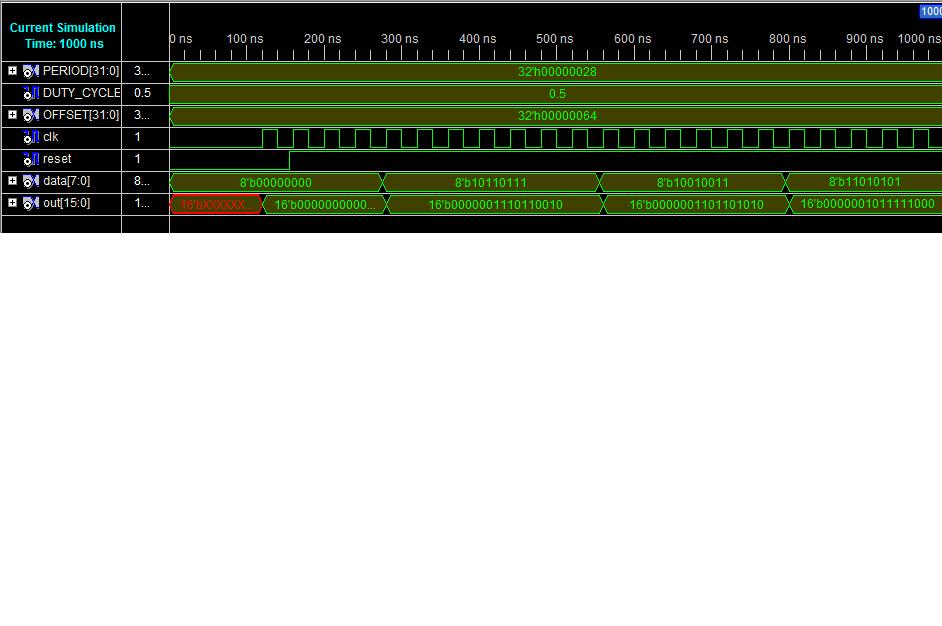

上代码中,只是实现输出了校验位,编码结果如何计算就不再啰嗦,相信大家都会了~~附上仿真图,如下:

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。